Poco a poco se acerca la comercialización de los procesadores basados en la nueva micro arquitectura de AMD prevista para el 7 de junio. Actualización: finalmente llegará al mercado en Septiembre según los últimos roadmaps.

Conforme pasan los días se va filtrando nueva información sobre su estructura interna y también algunos datos acerca de su rendimiento, o por lo menos del rendimiento de algunos Engineering Samples.

En este artículo hablaré sobre la estructura de la caché L3 en Bulldozer y sobre su funcionamiento.

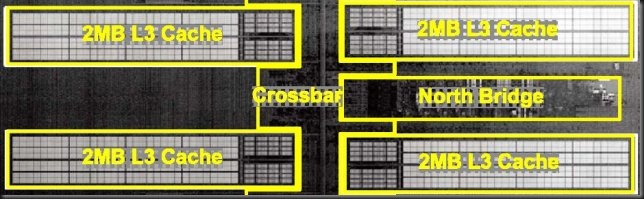

La caché L3 multibanco: 4 x 2 MB

AMD ha diseñado una caché L3 particionada en 4 sub arrays de 2 MB y 16 vías cada uno. la capacidad total en el chip de 4 módulos y 8 INT cores es de 8 MB y 64 vías de asociatividad.

El diseño es exclusivo, la L3 no incluye los datos presentes en la L2 de 2 MB de cada módulo y en cambio es una Victim Cache, donde se alojan las páginas desalojadas desde L2.

Con una frecuencia estimada en 2.4 GHz los anchos de banda son los siguientes:

- 307.2 GB/s en lectura gracias a sus dos accesos por ciclo de 128 bit y por módulo.2 400 000 ciclos/s x 4 módulos x (2 accesos/ciclo x 128 bit) = 2 457 600 000 bit / 8bits/1 byte = 307 200 000 bytes/s = 307.2 GB/s

- 153.6 GB/s en escritura gracias al acceso de 128 bit por ciclo.2 400 000 ciclos/s x 4 módulos x 128 bit = 1 228 800 000 bit / 8bits/1 byte =152 600 000 bytes/s = 153.6 GB/s

Por lo que se desprende de este documento, la caché L3 está conectada con cada módulo Bulldozer mediante dos buses de lectura de 128 bit y un bus de escritura de 128 bit. Se me antoja una mejora absolutamente espectacular respecto a anteriores diseños de AMD (un Phenom II X6, por ejemplo, solamente cuenta con un bus de 64 bit por core hacia y desde la L3 de 6 MB y 24 vías). De ahí sus mediocres resultados en este apartado.

Especulación 1. Espero latencias L3 elevadas en Bulldozer.

Teniendo en cuanta que la latencia efectiva L3 (load to use) es aditiva con la de los demás niveles y que la latencia L2 ya es conocida y va de los 18 a los 20 ciclos no será nada extraño que la latencia L3 efectiva en Bulldozer ronde los 50 ciclos.

Otro dato que apunta en la misma dirección es que se mantiene el diseño asíncrono con buffers de sincronización de Shanghai (Phenom II 45 nm), con una frecuencia de cores variable por los modos Turbo desde los 2.8 hasta los 3.5 GHz, será difícil conseguir bajas latencias L3.

Por último, una asociatividad tan elevada, 64 vías, aunque aumenta la tasa de aciertos L3, tampoco ayuda en cuanto a la latencia ya que hay que examinar 64 localizaciones cada vez en busca del dato o instrucción.

8 MB = 4 bancos de 2 MB y 16 vías

Una solución elegante que podría haber adoptado AMD consiste en que cada core tenga una latencia reducida de acceso hacia su banco local L3, es decir, que tenga “privilegio” de acceso a este banco y por ello mayor ancho de banda en GB/s y menor latencia en ciclos.

Esto sólo lo descubriremos en la práctica en cuanto le “echemos el guante” a un stepping final (comercial) de Bulldozer, lo tendremos el día 7 de Junio. Actualización: Bulldozer estará finalmente disponible en Septiembre si se cumplen las previsiones.

Conclusiones

AMD ha diseñado una caché L3 que marca un punto de partida desde sus actuales diseños de 45 nm y 6MB con 24 vías (Shanghai o Istambul). En Bulldozer son 4 bancos de 2 MB y 16 vías para un total de 64 vías.

Tengo ganas de probar un stepping final para ver si la latencia a cada uno de los bancos es diferente o por el contrario idéntica. Si existe una controladora de L3 para los 4 bancos será una latencia constante y elevada… en cambio, si cuenta (como Sandy Bridge) con una controladora L3 por cada banco de 2 MB pueden haber sorpresas.

En todo caso y con una L2 con 18 – 20 ciclos es difícil lograr latencias l3 muy recortadas. E s lógico esperar 10 ciclos más de latencia que en Sandy Bridge como mínimo (la L2 de SB tiene pipelines de 10 etapas Load to Use).

Destaca su optimización pensando en una baja disipación térmica y sobretodo en un consumo reducido, por ello su frecuencia rondará los 2.4 GHz y su voltaje estará sobre los 1.15 a 1.20 V efectivos. Es un diseño convencional, de bus con conectividad total entre todos los agentes, cada módulo Bulldozer y cada slice L3.

Hay que ser consciente del camino absolutamente divergente que ha adoptado Intel con Sandy Bridge 32 nm. La L3 es síncrona a los cores y funciona a la misma frecuencia que estos. Con ello consigue una bajísima latencia y un ancho de banda astronómico. Los diferentes bancos L3 se comunican entre sí mediante un ring bus bidireccional que aporta un gran ancho de banda y un funcionamiento “sencillo” a estos niveles.

Echad un vistazo a la web de mi nueva empresa, un proyecto de gran envergadura que llevo preparando hace más de un año.

Os lo recomiendo para diseño de sistemas de altas prestaciones optimizados al límite:

Allí tenéis a vuestra disposición el formulario de contacto, para consultas sobre este artículo hacedlo más abajo en la sección de comentarios.

Y mi nuevo Blog de contenido muy técnico y actualizado donde encontraréis artículos míos sobre hardware, procesadores y sistemas y también otros posts de expertos programadores e informáticos sobre otros temas de actualidad:

Si consideras útil el contenido de este Blog, ayuda a mantenerlo ojeando algunas de las ofertas que consideres interesantes de nuestros anunciantes.

No entiendo porque es que funciona a 2,4 GHz cuando los núcleos funcionan a una frecuencia hasta 1 GHz superior o mas en determinados casos (Turbo Core mediante) teniendo una latencia tan elevada.

ResponderEliminarAaaaaaaaah espera creo que me confundi entre latencia y etapas del pipeline.

Simplemente Bulldozer, a igualdad que pasados diseños de AMD (Barcelona, Shanghai, Istambul) o Intel Nehalem, es un diseño asíncrono.

ResponderEliminarLos cores funcionan a una frecuencia y voltaje y el uncore y la caché L3 a otra frecuencia distinta (menor) y voltaje menor.

Todo ello por consideraciones de disipación térmica, por rendimiento sería muy superior una implementación púramente síncrona como en Intel Sandy Bridge.

Un saludo,

Carlos Yus.

http://wccftech.com/2011/05/10/gigabyte-leaks-amd-bulldozer-details/

ResponderEliminarhttp://www.legitreviews.com/article/1501/11/

ummmmmmm

http://gadgetsteria.com/2011/05/25/amd-bulldozer-news-new-roadmap-and-more-benchmarks-leaked/

ResponderEliminarBulldozer FX 8130p (X8,L3 up 8MB,TDP 125W,3.8GHz+TCII 4.2)

Cinebench R10 mejor que el SB i7 2600K y peor que el Nehalem i7 990.

Cinebench R11.2 28074!!!!

Pcero,

ResponderEliminarTu primer link es un conocido fake, nada que ver con Gigabyte.

En cambio el segundo, merece más credibilidad, sería excelente para AMD que Bulldozer consiguiese esos resultados en CineBench...

Ojalá sea así, más competencia es lo que necesita el mundo X86. Hace ya 5 años que Intel domina a placer y quizás con Bulldozer haya algo más de juego.

En todo caso ten en cuenta que Intel lanzará en breve la plataforma LGA 2011 con CPUs de hasta 8 cores y 16 threads con 4 canales DDR3.

He visto roadmaps de AMD que citan un procesador de 6 a 10 cores Bulldozer para principios de 2012.

Si yo fuese AMD me iría a más cores para competir con Intel en gama alta.

También sería urgente (para más de 8 cores o 4 módulos) aumentar el número de canales DDR3 como en Magny Cours 12 C con su quad channel DDR3.

Veremos lo que nos deparan estos días de espera hasta el lanzamiento de Bulldozer.

Un saludo,

Carlos Yus.

Trinity

ResponderEliminarhttp://www.madboxpc.com/amd-trinity-detalles-oficiales-de-las-nuevas-apu/#comment-200321