AMD por fín comercializa los nuevos Phenom II, unos procesadores basados en el núcleo Shanghai de 45 nm, siendo el primer diseño de AMD en este nodo al que llega un año por detrás de Intel. Con él AMD retorna a la competición en prestaciones con su eterno rival Intel emparejándose a los Penryn quadcore Q9400 - Q9450 - Q9550.

AMD ha logrado reducir la superficie de Shanghai a 258 mm2 desde los 285 mm2 de Barcelona haciéndolo un procesador más barato de fabricar siendo similar a Core i7 (Nehalem) con sus 263 mm2.

Wafer de dies AMD Shanghai de 45nm.

Ya hace un tiempo indiqué las prestaciones esperadas y las nuevas características que hacían de Phenom II un procesador clave para AMD:

" Un AMD Phenom II 940BE a 3 GHz tendrá prestaciones similares a un Phenom actual a unos 3.5 - 3.6 GHz. En Fritz Chess Benchmark espero índices sobre los 8500 - 9000 puntos. Es decir, sobre la velocidad de un C2Q 9450 o 9550, lo cual para AMD es todo un salto en prestaciones (un Phenom 9950BE obtiene unos 6100 puntos). "

Con Phenom II, AMD ha dejado atrás el fatídico nodo de 65 nm. Todos los diseños de AMD en este nodo han sido un fracaso relativo ... Recordemos el core Brisbane A64 X2 o el propio Barcelona quadcore ...

Perspectiva del die Shanghai.

Ahora que se conocen con más detalles los refinamientos de Shanghai sobre Barcelona los comentaré más en mayor profundidad:

-

La caché L3 compartida aumenta hasta los 6 MB desde los exiguos 2MB de Barcelona.

-

-

Proceso de fabricación de 45 nm con litografía de inmersión lo que proporciona mayor potencial de reloj, menos disipación térmica y menor consumo respecto al anterior proceso de 65 nm de Barcelona.

-

Según AMD la L3 de Shanghai es 2 ciclos más rápida en acceso que la de Barcelona (Phenom).

-

Cuando un núcleo entra en estado de ahorro energético los contenidos de las cachés L1 y L2 se mueven a la L3 compartida permitiendo una detención total del reloj (

clock gating).

-

Por fín AMD implanta predicción de saltos indirecta.

-

Se dobla el ancho de banda de probe (chequeo datos/instrucciones en cachés L1 - L2).

-

Mayores buffers load y store en las controladoras de memoria.

-

Mayores buffers de coma flotante.

-

Reducción del tiempo MAB (missed buffer).

-

Mejora del pipelining de prefijos de instrucciones LOCK.

-

Optimización del movimiento entre registros de coma flotante.

Un primer plano de Shanghai en el que destaca su L3 de 6 MB.

La caché L3 de Shanghai

Tamaño:

El aumento de la L3 a 6 MB es el rasgo fundamental de la transición Barcelona 65 nm a Shanghai 45 nm. Barcelona era un procesador claramente falto de caché L3, 2 MB para 4 núcleos es claramente insuficiente y realizando profiling podemos comprobar que los 6 MB de Shanghai mejoran mucho las cosas pero todavía queda terreno a la mejora.

Un tamaño doble en una caché reduce los fallos de caché (caché miss) en un factor 1.4 (raiz cuadrada de 2), eliminando así costosos accesos al nivel siguiente de caché o si es el LLC (last level cache), en este caso L3, lentísimos accesos a memoria (del orden del 150 - 200+ ciclos).

Asociatividad:

La asociatividad de 48 vías es sorprendente. Intel utiliza una L3 de 8 MB y asociatividad 16 en Core i7. A mayor valor mejor tasa de aciertos debido al soporte de cargas de trabajo con menor localidad espacial en memoria.

48 vías significa que una posición de memoria se puede cachear en 48 posiciones diferentes de caché. Pero esto implica que cada vez que hay que buscar una posición de memoria en caché L3 hay que buscar en 48 líneas de caché, lo que obviamente hace el acceso L3 más lento.

Una asociatividad doble reduce la tasa de fallos de caché igual que lo haría un tamaño de caché doble, es decir en un factor 1.4. Aunque para asociatividades elevadas (más de 8) la mejora es cada vez menos importante.

Los integrantes iniciales de la gama Phenom II:

-

Phenom II 920: 2.8 GHz, 1.8 GHz L3/IMC, 3.6 GHz HT. Unos 270 €.

-

Phenom II 940: 3.0 GHz, 1.8 GHz L3/IMC, 3.6 GHz HT. Unos 230 €.

Lamentablemente, y debido a razones de consumo y disipación, AMD ha tenido que dejar a la L3 y las IMC (Controladoras de memoria integradas) a una frecuencia de solo 1.8GHz.

Por ejemplo, el actual Phenom 9850 y el 9950 utilizan una frecuencia L3/IMC de 2.0GHz. Esta reducción en Shanghai aumentará la latencia relativa de la L3 y la memoria principal, aunque gracias a las mejoras microarquitecturales introducidas será en la práctica más rápida que la de Phenom Barcelona.

Hay que tener en cuenta que Shanghai es el primer procesador de AMD fabricado en 45 nm y que sin duda mejorará con el tiempo. De hecho, las nuevas versiones AM3 de Phenom II previstas para Febrero implantan una L3/IMC a 2.0 GHz para soportar DDR3 1333, aunque supondrá un cuello de botella en la arquitectura (un dual channel DDR3 1333 requeriría un reloj de IMC/L3 de 2.66 GHz para asumir el ancho de banda proveniente de los módulos con la actual implementación de bus L3 de solo 64 bit bidireccional). Explicado aquí.

A modo de apunte, los Opteron basados en el core Shanghai, tienen la L3/IMC a 2.2 GHz lo que les aporta un plus prestacional y compiten muy favorablemente con toda la gama Xeon Quadcore de Intel.

Prestaciones

Phenom II mejora a Phenom de un 5 a un 30% a igualdad de reloj según la aplicación debido a sus numerosas mejoras microarquitecturales y sobretodo a su L3 de 6 MB y 48 vías.

En el terreno de los juegos la mejora llega en algunos títulos a un 50% del Phenom II 940 (3.0 GHz) respecto al Phenom 9950 (2.6 GHz).

Yo esperaba prestaciones en el entorno de un C2Q 9450 o un C2Q 9550, pero debido al bajo reloj L3/IMC de 1.8 GHz (yo esperaba 2.2 GHz), más bien estarán en el entorno del C2Q 9400 o C2Q 9450.

Consumo y disipación térmica

El TDP de Phenom II está situado en 125W, un valor respetable. Este alto consumo es debido a la juventud del proceso de 45 nm de AMD - IBM lo que obliga a utilizar voltajes elevados (1.35 V en al 940) que aumentan considerablemente la producción de calor.

CPUZ nos muestra los 1.35 V nominales del Phenom II 940.

-

La disipación térmica crece linealmente con la frecuencia: Doble frecuencia, doble consumo, doble disipación.

-

En cambio, al aumentar el voltaje, el consumo y la disipación crecen con la tercera potencia (el cubo) del voltaje: doble voltaje, ocho veces mayor consumo y disipación térmica.

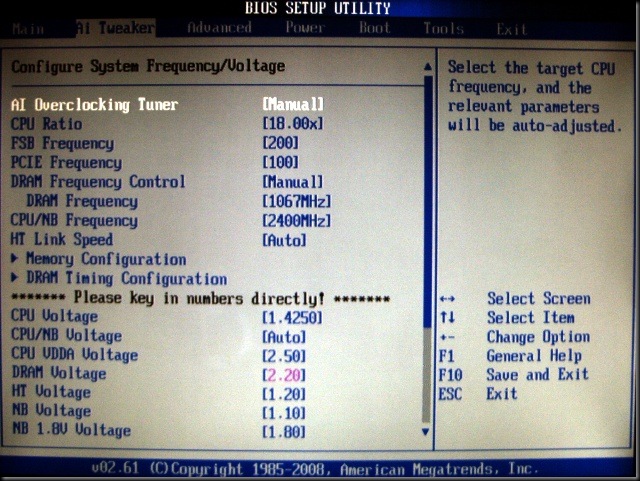

Overclock

Dependiendo de cada procesador en particular (siempre hay variaciones) podemos esperar un overclock estable con refrigeración por aire en unos 3.4 GHz y con un excelente cooler podemos llegar a los 3.5 - 3.6 o incluso 3.8 GHz donde entramos ya en la refrigeración líquida que puede extenderse hasta los 4.0 - 4.4 GHz (como máximo).

El futuro

AMD no disipa las dudas sobre la microarquitectura que seguirá a Shanghai, los detalles son escasos y no entraré a comentarlos.

Lo que sí haré es una lista de "deseos" en la que plasmo lo que creo que AMD podría implantar de cara a aumentar el IPC (instructions per clock) en su nuevo núcleo:

-

Aumento de la asociatividad de la L1i (caché de instrucciones de nivel 1). Las actuales cachés de 64 KB y 2 vías tienen una alta tasa de fallos debido a su bajísima asociatividad (Intel utiliza un diseño de 8 vías) pese a su gran tamaño. Realizando

profiling se ve claramente la menor tasa de fallos de la L1i de Core2 (32KB, 8 vías) frente a la L1i de Phenom o Athlon64 (64KB, 2 vías) pese a su menor tamaño.

-

Aumento del ancho de ejecución a quad issue.

-

Mejora del mediocre mecanismo de branch prediction (en comparación con Core2 o Core i7).

-

Implantación de desambiguación en escrituras y lecturas combinadas en memoria.

-

Aumento del ancho del bus IMC/L3 - cores a 128 bits bidireccional.

-

Reducción de la latencia L2 de los actuales 15 ciclos aunque ello signifique una reducción de su tamaño a 256 KB hasta niveles similares a Core i7.

-

Reducción de la latencia L3 mediante mejora en los timings de sincronización y aumento de su frecuencia base (actualmente 1.8 - 2.0 - 2.2 GHz).

-

Aunque a AMD le desagrade, inclusión de los nuevos juegos de instrucciones Intel SSE4 y futuros.

-

Aumento del tamaño L3 sin aumentar desmesuradamente la asociatividad.

-

Introducción de SMT de dos vías al estilo Intel HyperThreading.

Espero ver plasmadas alguna de estas ideas en los futuros diseños (que ya estarán seguramente ultimados, al menos en la mesa de diseño) del fabricante alemán.