Estos días Intel está celebrando en San francisco el IDF 2010 (Intel Developer Forum), entre multitud de temas relacionados con el futuro de la industria de semiconductores ha hablado de Sandy Bridge.

En estos artículos me voy a centrar en los cambios microarquitecturales de Sandy Bridge sobre la anterior generación de cores de Intel, Nehalem 45 nm y Westmere 32 nm.

En esta primera parte abordaré varios aspectos:

- Intel Tock 2010. La aplastante cadencia del gigante de los semiconductores.

- Sandy Bridge Ring Bus. La nueva organización de la comunicación inter die.

- El System Agent de Sandy Bridge. El Uncore o North Bridge.

- El Front End de Sandy Bridge. Las primeras etapas del pipeline.

- El mecanismo de Branch Prediction, tan críticamente importante en algoritmos de enteros.

Intel Tock 2010

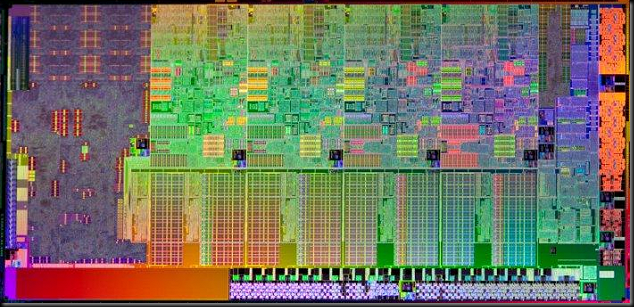

Sandy Bridge es un cambio profundo respecto a la ya excelente y exitosa microarquitectura que Intel puso en juego en 2008 con Nehalem, los cores que mueven los chips Core i7.

Poco había que mejorar en la arquitectura de los cores Nehalem, ya que Intel lidera en prestaciones en todos los campos… pero los grupos de ingeniería en Intel no podían quedarse dormidos en los laureles (como desafortunadamente hizo AMD tras su excelente core K8).

Por ello han procedido a un exhaustivo y profundo rediseño:

Desde el Front End, hasta las unidades de ejecución, el Branch Prediction e incluso las unidades Load – Store. También se ha modificado la arquitectura de la cache L3 dividiéndola en bancos de 2 MB por core y la interconexión interna de las diferentes partes del procesador.

El Ring Bus que ahora hace de ruta de comunicación entre todas y cada una de las partes del procesador:

- cores

- Bancos de L3 de 2 MB

- System Agent -Uncore o North Bridge-

- GPU integrada

- Video decoder – encoder

Es, a mi modo de ver, uno de los cambios más significativos respecto a diseños anteriores (Westmere y Nehalem).

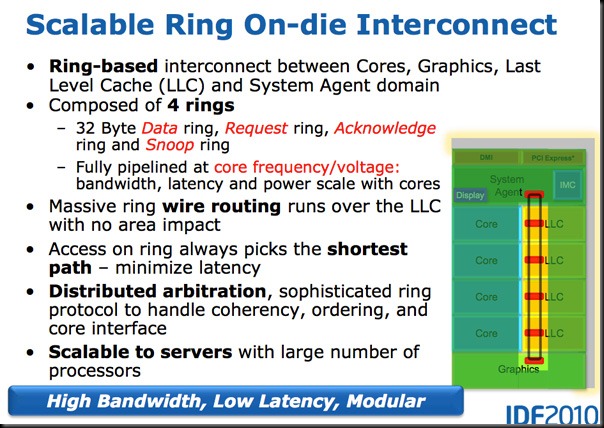

Sandy Bridge Ring Bus

Intel ha dotado a Sandy Bridge de un novedoso y extremadamente rápido sistema heredado de su hermano mayor Nehalem EX, un anchísimo y eficiente Ring Bus de comunicaciones para coordinar todas las transacciones de datos inter die.

El ancho de banda del bus de datos es de 32 bytes, es decir, 256 bits y su topología es en anillo, es decir, escala con el número de cores y bancos de L3. A mayor número de cores o bancos de L3 mayor ancho de banda agregado.

Lo más llamativo del bus en anillo de Sandy Bridge (y Nehalem EX) es su implementación respetuosa con el consumo y el área de die, me explico:

Todos recordamos el famoso procesador Radeon HD 2900 de ATI con un ring bus de 512 bits, que debido a su desmesurada disipación térmica y consumo no pudo competir con sus análogos de nVidia hasta que ATI lo eliminó sustituyéndolo por una arquitectura convencional en su serie Radeon HD 3800.

En Sandy Bridge Intel ha utilizado power gating y clock gating extensivamente, además de aplicar un voltaje bajísimo al ring bus para conseguir una disipación térmica muy baja.

Por otro lado, es un dato muy importante, según los ingenieros de Intel, no ha representado un incremento de área ya que la infinidad de conductores necesarios para el Ring Bus se enrutan por otras capas del diseño bajo la caché L3.

Lo que se consigue con este ring bus es aumentar de manera lineal el ancho de banda agregado (total) con el número de Ring Stops (cores, bancos de L3, …) consiguiendo una escalabilidad perfecta.

Como he comentado en artículos anteriores, además se consigue una muy notable bajada de latencia de la caché L3, del orden del 30% (!!) que ya de por sí en Nehalem y Westmere era realmente rápida.

Ahora nos encontramos en los veintitantos ciclos de latencia respecto a los 38 - 42 ciclos de Nehalem y algo más en Westmere.

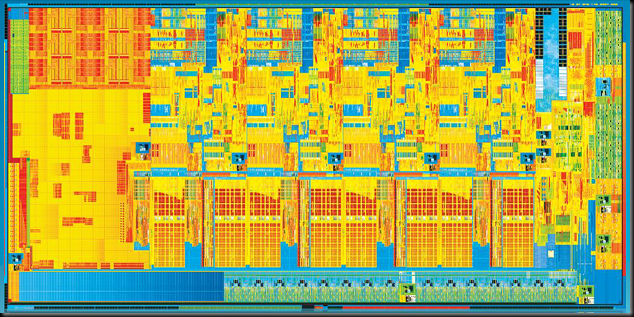

El System Agent de Sandy Bridge

El anteriormente denominado Uncore, Nocore o North Bridge ahora no incluye ya la caché L3, por lo que la L3 es síncrona a los cores, con lo que aumenta su frecuencia aumentando su ancho de banda y disminuye su latencia.

El System Agent se encarga de controlar todas las transacciones entre los cores, la GPU integrada, los coders y decoders de video integrados con:

- La memoria principal a través de las dos controladoras DDR3.

- Las GPUs externas a través de los puertos PCI Ex.

- Los dispositivos externos a través del DMI vía chipset.

Para mejorar la disipación térmica y reducir el consumo en sistemas portátiles integra la controladora de video y la PCU (Power Control Unit) encargada de gestionar los voltajes y las frecuencias de los cores así como los Turbo Modes y los modos de ahorro de energía y el Power Gating a nivel de cores.

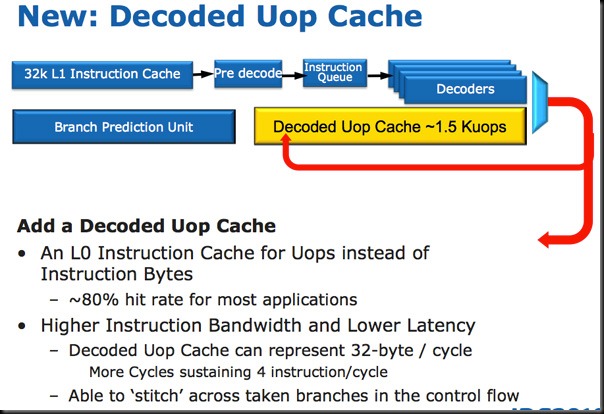

El Front End de Sandy Bridge

El Front End es la parte del microprocesador encargada de suministrar la secuencia de instrucciones X86 desde la caché L1i (cache L1 de instrucciones) y de descodificarlas a un formato más manejable (micro operaciones, uops).

Intel, en este apartado ha roto con el pasado y ha desarrollado un Front End revolucionario.

Estas instrucciones ya descodificadas se encuentran en un formato interno y propietario, son llamadas uops (micro operaciones) y son características de cada microarquitectura.

Sandy Bridge mejora el Loop Stream Buffer de Westmere 32 nm que contenía hasta 28 uops con una estructura dedicada llamada Decoded uop Cache que es capaz de almacenar unas 1500 uops (sobre unos 6 KB de capacidad) y que actúa a modo de caché L0 de instrucciones suministrando a las etapas de ejecución fuera de orden instrucciones con menor latencia que la L1i de 32 KB y además manteniendo más fácilmente la cadencia de 4 uops / ciclo.

Además el Fetching desde esta nueva L0i se hace en paquetes de 32 bytes / ciclo, aumentando el llenado efectivo de las unidades de ejecución que le siguen en el pipeline.

Intel cita la tasa de aciertos de esta L0i en un 80% en código de aplicaciones típicas. En el caso de acierto (que como vemos es un 80% de las veces) se desconectan las etapas de Fetch y Decoding con el consiguiente ahorro energético y de temperatura (muy notable ya que el consumo de estas etapas es muy alto en CPUs de arquitectura X86).

Entre los mecanismos que forman parte integral del Front End nos encontramos con la lógica y SRAMs de Branch Prediction encargado de cargar en el orden correcto la secuencia de instrucciones después de una bifurcación en el código (Branch) decidiendo si la condición se cumple o no mediante lógica y algoritmos de especulación y distintas tablas de datos de historia precedentes.

El mecanismo de Branch Prediction

Sandy Bridge ha mejorado notablemente el manejo de Branches en el código, aumentando la tasa de acierto. Los ingenieros de Intel han optimizado el diseño pero permaneciendo en el misma footprint (la misma superficie).

Utilizando técnicas de compresión sin pérdidas en Sandy Bridge se almacenan más datos de historia en la misma capacidad que en Westmere por lo que efectivamente se han ampliado al doble el número de entradas en las tablas de Targets, elevando con ello la tasa de aciertos de los algoritmos respecto a Westmere.

Estoy deseando probar Sandy Bridge en algoritmos ajedrecísticos.

Nos vemos en la segunda entrega.

Si consideras útil el contenido de este Blog, ayuda a mantenerlo ojeando algunas de las ofertas que consideres interesantes de nuestros anunciantes.

Enhorabuena Carlos por la entrada, manteniendo tu linea de precisión y sensillez al mismo tiempo en la redacción de tus artículos.

ResponderEliminarSupongo que en la segunda o tercera parte hablarás de los cambios y limitaciones del overclock en esta nueva arquitectura. ;)

Un saludo, y te animo a que sigas mucho tiempo con tus blogs.

Saludos dPUNiSH3R,

ResponderEliminarEn primer lugar, te agradezco tus ánimos, es agradable ver que estos temas atraen a un volumen ya respetable de aficionados al hardware.

Sobre las limitaciones de OC impuestas por Intel para los procesadores Core i3 / i5 / i7 basados en la nueva microarquitectura Sandy Bridge debo decir que afectarán a las versiones bajas.

Está previsto que por unos 200€ - 250€ hayan veriones K de los quad core, con multiplicador desbloqueado, en todo caso veremos cuando en 2 - 3 meses salgan al mercado.

Sinceramente, espero que Intel no sea excesivamente celoso en este aspecto y libere muchos procesadores en OC mediante multiplicador.

Un saludo,

Carlos Yus.

Carlos tengo una duda existencial a ver si tu eres capaz de resolvermela. Supongamos que tenemos un procesador con 2 nucleos monohilos y un procesador mononucleo con dos hilos. Cómo funciona a nivel de ejecución? Sé que con dos hilos es como si ejecutaras dos procesos a la vez, pero no sería lo mismo con dos nucleos?

ResponderEliminarun saludo

Alberto, un procesador dual core son dos procesadores independientes en un die (en un mismo chip).

ResponderEliminarEn cambio un procesador SMT, es decir, dual threaded es un único procesador que ejecuta por simultáneamente dos threads. Para ello tiene algunas estructuras internas duplicadas por threads y otras particionadas o compartidas por ambos threads. El secreto está en conseguir un tiempo de ejecución de ambos threads simultáneamente (SMT) más corto que su ejecución en serie.

En los procesadores Core i7, en casi todos los casos resulta más rápido el modo SMT que el modo single threade. Las pocas excepciones las representa software3 limitado principalmente en las etapas de ejecución.

Un saludo,

Carlos Yus.