En este artículo voy a ilustrar dos conceptos:

- El concepto de procesador SMT (Simultaneous Multithreading) utilizado hace años por Intel, primero en su línea Netburst y actualmente con sus brillantes CPUs Nehalem 45 nm ,Westmere 32 nm y próximamente en 2011 Sandy Bridge (32 nm).

- El nuevo diseño CMT (Cluster Multithreading) utilizado por AMD en sus futuros procesadores basados en la microarquitectura Bulldozer para 2011.

Empiezo primero por el concepto de SMT utilizado por Intel en su tecnología HyperThreading, el lector impaciente puede avanzar más abajo para ver la implementación de CMT en AMD Bulldozer.

SMT (Simultaneous Multithreading)

SMT es un concepto nacido con el fin de ocupar al máximo y durante el mayor porcentaje de tiempo posible los recursos de proceso de un procesador, esto se logra ejecutando simultáneamente dos o más threads en un único core.

De nada sirve un core con 8 ALUs de proceso de enteros si no hay instrucciones suficientes para llenarlas o si estas instrucciones necesitan datos que no están todavía disponibles para la ejecución.

Intel, durante el desarrollo de su primer procesador Pentium 4 (microarquitectura Netburst) se dio cuenta de que muchas de sus unidades de ejecución (ALUs, AGUs, FPUs) estaban un porcentaje significativo del tiempo de ejecución de un programa desocupadas, en reposo por falta de instrucciones o datos.

Esto era debido principalmente a tres hechos:

- L1d Cache mises: Fallos de caché L1d (datos). Si queremos sumar dos números, deberemos conocer esos números antes de ejecutar la instrucción suma sobre los datos. Si los datos no están en la caché L1d, el procesador deberá chequear la caché L2 debiendo esperar en circunstancias reales un mínimo absoluto de 10 ciclos en un P4 Willamette 180 nm o Northwood 130 nm.

- Branch missprediction: Fallo en la predicción de saltos. Los procesadores, desde hace décadas intentan averiguar dónde va a “saltar” la ejecución del programa para tener ya esas instrucciones preprocesadas. Este mecanismo consigue aumentos notables de velocidad de proceso aunque en caso de fallo en la predicción (sobre un 5 % en CPUs modernas) se produce un vaciado de los pipelines de instrucciones y una reejecución de las mismas con la consiguiente penalidad en rendimiento.

- Falta de ancho de banda del decoder que de la trace cache en caso de Trace Cache Miss: La trace cache era capaz de suministrar tres instrucciones / ciclo a las unidades de ejecución pero en caso de no encontrarse la instrucción en la TC se daba un TC Miss. Lamentablemente, y era una increíble limitación del diseño Netburst, el decoder previo a la TC solo introducía instrucciones decodificadas a un ritmo de una por ciclo. Absolutamente insuficiente, cualquier CPU de su época decodificaba 3 instrucciones / ciclo (Pentium III, AMD Athlon).

La Trace Cache de Pentium 4 Northwood 130 nm.

La Trace Cache de Pentium 4 Northwood 130 nm.

Las dos primeros causas de desocupación en las unidades de proceso se resolvian, al menos parcialmente gracias al SMT. Sobre el diseño de la TC, no tenía solución y lo dejo para otro artículo futuro…

SMT consiste en ejecutar a la vez dos threads de una misma aplicación o de dos aplicaciones diferentes en un core. Para ello se deben de rediseñar muchos aspectos del procesador de dos modos:

- Hay partes del core que se deben de duplicar por thread.

- Otras estructuras deben particionarse.

Estas partes de la CPU a duplicar o particionar comprenden todas las zonas de almacenamiento de código y datos del procesador:

- Es necesario duplicar el número de registros arquitecturales y de registros renombrados por thread.

- Se deben de dimensionar al alza todas las colas (queues) de instrucciones del procesador para asegurar espacio para dos threads distintos y que la lógica de procesamiento fuera de orden (OOO Logic) tenga suficientes instrucciones dentro de la ventana (OOO window) listas para ejecutar y mantener las etapas de ejecución llenas.

- Todo esto debe hacerse con un sistema que prevenga y evite la competencia por los recursos entre los dos threads, para evitar problemas de rendimiento.

Todo ello conlleva una cantidad de hardware adicional (transistores) estimada entre un 5 y un 10% del área del procesador.

La buena noticia es que el SMT aumenta de forma típica el rendimiento de un core de un 10 a un 70% en función del código.

En Pentium 4 yo medí en múltiples ocasiones sobre un 30% de mejora con Hyper Threading habilitado. En Core i7 la mejora es todavía superior.

CMT (Cluster Multithreading) en AMD Bulldozer

El concepto CMT es la respuesta de AMD al SMT de Intel: Hyper Threading.

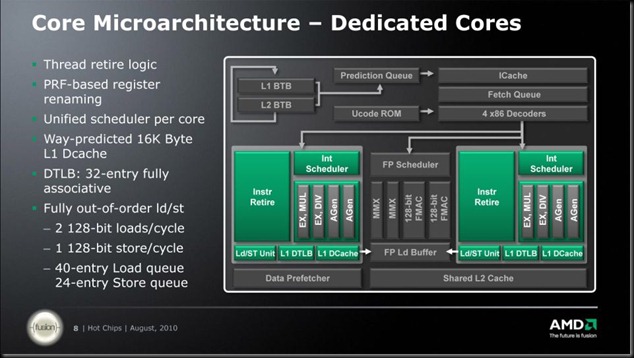

AMD llama a cada conjunto de 2 INT cores y 1 FPU compartida (más las cachés L1 y otra circuitería) un módulo.

CMT consiste en duplicar algunas de las unidades de ejecución para conseguir con ello un aumento de prestaciones a la vez que se comparten algunas unidades que por su tamaño no es práctico duplicar.

En el caso de Bulldozer 32 nm, AMD ha diseñado un procesador dotado de dos cores de enteros (INT cores) compartiendo:

- El hardware de Branch Prediction.

- La caché L1i de instrucciones de 64 KB y 2 vías.

- Las etapas de fetch (32 bytes / ciclo).

- Los cuatro decoders X86.

- La FPU dual de 128 bit FMAC:

También son compartidos los siguientes componentes del die de Bulldozer:

- El Data Prefetcher encargado de precargar datos en las caches.

- La caché L2 compartida para cada dos INT cores con su L2 TLB.

En Bulldozer, al haber dos cores de enteros completos, hay muchas estructuras duplicadas:

- Un scheduler de enteros (INT scheduler) por core, unificado para ALUs y AGUs.

- Dos ALUs. Unidades de proceso de enteros.

- Dos AGUs. Unidades de generación de direcciones de memoria.

- L1d de 16 KB y alta asociatividad.

- L1 DLTB de 32 entradas fully associative.

- Juego de registros y de registros alias con su hardware de renombramiento.

- Unidad de Load - Store con procesamiento fuera de orden en lecturas y escrituras a memoria con sus colas de comandos.

La verdad es que es una cantidad de circuitería notable a duplicar, aunque AMD afirma que la superficie del procesador no ha aumentado demasiado por ello.

Según AMD, la mejora de prestaciones en enteros gracias a integrar un segundo core en el módulo ronda el 80%.

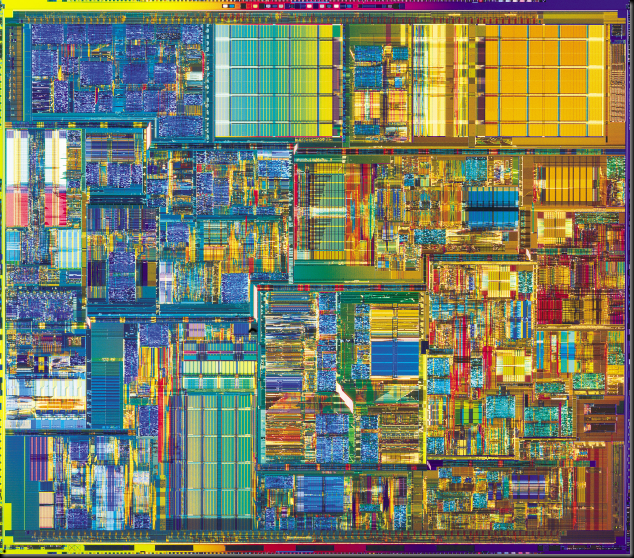

En cuanto haya disponibles fotografías del die de Bulldozer veremos cuanto hay de cierto en ello y ya en 2011 cual es la competitividad real de este nuevo diseño.

En cualquier caso me es llamativa la reducción de 3 a 2 ALUs y AGUs por INT core de Phenom II a Bulldozer que puede acarrear reducción de rendimiento single threaded, aunque creo que será compensada con los demás avances a nivel de core.

Echad un vistazo a la web de mi nueva empresa, un proyecto de gran envergadura que llevo preparando hace más de un año.

Os lo recomiendo para diseño de sistemas de altas prestaciones:

Allí tenéis a vuestra disposición el formulario de contacto, para consultas sobre este artículo hacedlo más abajo en la sección de comentarios.

Y mi nuevo Blog de contenido muy técnico y actualizado donde encontraréis artículos míos sobre hardware, procesadores y sistemas y también otros posts de expertos programadores e informáticos sobre otros temas de actualidad:

Si consideras útil el contenido de este Blog, ayuda a mantenerlo ojeando algunas de las ofertas que consideres interesantes de nuestros anunciantes. Gracias de antemano.

El que tenga dudas o aportaciones tiene para ello la sección de comentarios, intentaré responder a todos y con la máxima claridad. Los Blogs deben de ser lugares de intercambio y agradezco vuestro feedback.

![ip16_texto_300px_blanco[4][2][2][2] ip16_texto_300px_blanco[4][2][2][2]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEj2AB0bHrn32lL_MmgAl3LAvhZVml4gA7daqausofxu9y26FYW8KZqKTOa_j-f5HviWcWE2VeINEIdt9oMMbHr9Xc0GCegJSJgjMTJ2WrJy8Sj0pPD4fXeMwOD-CknUGcO81lZ95szRl_o/?imgmax=800)

![infromaticapremium-blog[4][2][2][2] infromaticapremium-blog[4][2][2][2]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEjxLM2NN6Fw1zg33bGlz30FfU-KLI43BZLIR3l80wsQQ-i_EUIB4WfcEXLqJRsDpvzBmQg4E7UwPBjkYuai0_5eM8Vkud_VyP2xkn3TvrR5HCyzyqjfp0kACQzvwN-Ix9oCTXfZUQubjOg/?imgmax=800)

Muchas gracias por la explicación, sobre todo de la parte en que se detallan los errores del HT del Pentium IV, ahí muestras como funciona un procesador, o mejor dicho cual es el orden en el que se van manejando los datos y las instrucciones. Si tuvieras algún link donde se explique sobre este tema, versión para Dummies, lo agradecería mucho

ResponderEliminarBuena info. No son ALU's ni AGU's exactamente. Son AGLU's ¿raro no?. Pero bulldozer ha intruducido, muchos conceptos nuevos. Es por eso que puede ejecutar cada hilo o núcleo 4 instrucciones enteras de 64bits por ciclo.

ResponderEliminarEn teoría las AGLUs combinan la funcionalidad normal una AGU (cálculo de direcciones de memoria) con algna capacidad de cálculo lógico ALU (Arithmetic Logical Unit).

ResponderEliminarEstá por ver hasta que punto es eso cierto, soy bastante escéptico en ese aspecto.

Incluso en el "tosco" y mal redactado manual de AMD en el que detalla la arquitectura de Bulldozer no menciona que sean útiles para mucho más que cálculo AGU y algunas formas de LEA.

Un saludo,

Carlos Yus.