Ayer expiró la NDA referente a la publicación de las primeras imágenes, aunque de bajo detalle, del octal core nativo Nehalem-EX. En este artículo esbozo algunas peculiaridades y característica de este nuevo procesador que se comercializará a finales de año.

Que nadie se lleve a engaño pues jamás tendremos un procesador Beckton en nuestro sistema personal, está diseñado con otras cargas de trabajo en mente e incorpora tecnologías RAS (novedad en el mundo X86) de la familia Itanium.

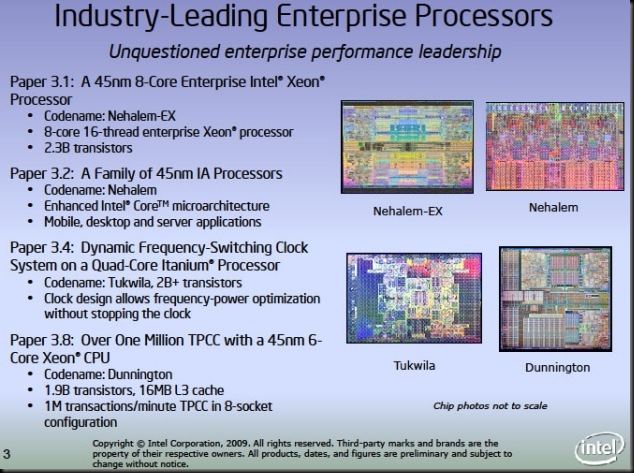

En la captura superior apreciamos Nehalem-EX junto a Nehalem y debajo Tukwilla (Itanium quad core de 65 nm) y Dunnington (Xeon hexa core nativo con 16 MB L3 basado en núcleos Penryn de 45 nm).

Hace unos meses (en diciembre de 2008) realicé un análisis muy arriesgado, aunque iba bien encaminado, del die de Beckton basándome en las muy lejanas y de mala calidad fotografías de un wafer de procesadores que sostenía un orgulloso Patrick Gelsinger. y no era para menos.

![[Gelsinger_Beckton3.jpg]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEjpOx_DBB8lVRmmKpg5i48Vu7WVegOV7_uyHfdDahIvuQg_HAWbL6GLH6x_93U2S4krbuvgrlMUTM7r3qbp8hFqHuJy-llf8hyphenhyphen4OHJmedVS2zUXw17f3syRE4EaVfqJ6OFPlumGfsPG5V8/s1600/Gelsinger_Beckton3.jpg)

2.3 millones de transistores en 45 nm

Beckton constituye un procesador monstruoso, 2.3 millones de transistores para:

- Ocho núcleos de arquitectura Nehalem con SMT de dos vías.

- 24 MB de caché L3 distribuidos en bancos independientes.

- 4 enlaces QPI.

- 4 controladoras de memoria DDR3 asociadas a chips externos (SMB, Scalable Memory Buffer).

La elección de los arquitectos de procesadores de Intel de implementar una caché de tercer nivel de 24 MB ya posiciona de por sí el producto orientándolo hacia cargas de trabajo de servidor.

En Beckton 24 MB son 3 MB por núcleo (o 1.5 MB por thread), un paso adelante desde Nehalem con sus 2 MB por core. Bien es cierto que una caché de tal magnitud no puede tener unos tiempos de acceso fulgurantes, pero en entorno servidor esto es menos importante que acceder constantemente a memoria y más todavía a memoria no local.

Además, recordemos que la función del LLC (Last Level Cache), en este caso la L3, es también evitar tráfico de coherencia de cachés de niveles inferiores.

Análisis del die

Como vemos, los núcleos han pasado a la periferia en grupos de dos colocados simétricamente respecto al centro del chip. Es una buena opción para evitar hot spots térmicos distribuyendo mejor la generación de calor en el procesador (como es sabido las cachés consumen comparativamente muchos menos W/cm2 que la lógica).

La superficie estimada ronda los 600 mm2, partiendo de los 246 mm2 del actual Nehalem quad core que encontramos en los procesadores Core i7.

Los núcleos serán prácticamente idénticos a los conocidos de Nehalem en los Core i7, con SMT de dos vías para un total de 16 threads por chip y por socket. Las cachés L1 y L2 serán respectivamente de 32 + 32 KB y 256 KB la L2 de baja latencia (exacto a Core i7).

En la parte superior de die encontramos los cuatro enlaces QPI para comunicación con otros procesadores y con el chipset o IO Hub.

En la parte inferior se sitúan las controladoras de memoria que se conectan a cuatro procesadores externos llamados SMB o Scalable Memory Buffer que permitirán hasta 16 (!!) DIMMs por socket.

En el centro encontramos la interfaz de sistema, el antiguamente llamado North Bridge, que incluye toda la lógica y buffers de comunicación con el exterior, en este caso habrá variaciones muy importantes respecto a Nehalem por las funcionalidades RAS añadidas para acceder a mercados hasta ahora reservados a procesadores Itanium o competidores RISC como IBM Power y otros.

Debo decir que han hecho un buen trabajo ocultando detalles en las fotografías… a juzgar por ellas todos los sub arrays de 3 MB (hay ocho de ellos) son morfológicamente idénticos. Veremos con el tiempo qué estructura interna ocultan, aunque en la fotografía inferior ya se aprecian más claramente y parecen bloques típicos de caché:

En esta fotografía se aprecian mejor los ocho núcleos Nehalem y sobretodo los ocho arrays de caché L3 de 3 MB para un total de 24 MB. Nótese la gran cantidad de lógica adicional a lo largo del centro del die.

Intel podrá, en caso necesario desactivas independientemente núcleos defectuosos o arrays de L3 de 3 MB que presenten defectos funcionales.

Frecuencias esperadas de Nehalem-EX

Lógicamente, un octal core nativo compuesto de 2.9M de transistores, debe de ir limitado por TDP, lo que nos indica que inicialmente no veremos los 3 GHz. Lo esperable son frecuencias sobre los 2.13 – 2.26 GHz, quizás con los topes de gama a unos 2.66 GHz.

![isscc_05[1] isscc_05[1]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEjNhx7gEAY3oKJjg2HboRq8wPAfaD8kKKWDfLoU62HQqaOgFQT36TJbG0FGyOyg5SHN0GUhXPY760suZh-ANdTULSQOh7yG0xzxdeqsirt7iuaCCLT6eBrjS2nAmx1oku1D0YlJAW5t3oE/?imgmax=800)

Intel, como era de esperar dada su maestría en estas lides, ha desarrollado un nuevo proceso de fabricación de 45 nm específico para Beckton con un Leakage menor, permitiendo frecuencias superiores que si se tratase simplemente de dos dies Nehalem en un chip más la lógica adicional y con 24 MB de L3.

Estará disponible a finales de este año para servidores de alta gama, y especialmente utilizado en virtualización, además al incorporar características RAS dotará a estos entornos de una robustez añadida nunca vista en la arquitectura X86.

Podrá no solo detectar sino aislar y corregir errores tanto de procesamiento como de memoria o I/O.

Un gran avance, sin duda. Y 24 MB de caché L3, bff, los accesos a memoria principal serán bastante anecdoticos con rescpecto a las CPU de desktops.

ResponderEliminarNo controlo mucho de arquitecturas, pero no sería más óptimo implementar una L3 con caché compartida por cada uno de los 4 pares de núcleos pongamos de 2MB y finalmente una L4 más equilibrada en cuanto a tamaño?

Supongo que no lo harán por temas de afinidad en los datos que maneja cada core en servidores o algo así (a parte de los costes de un nivel más de caché "rápida"), que opinas?

Un saludo.

PrT, un comentario interesante.

ResponderEliminarSin duda alguna, la implementación elegida es la óptima. Los equipos de ingenieros de intel han realizado simulaciones de todas las combinaciones posibles de L3 discretas para 4 + 4 núcleos y cachés L4 compartidas... el rendimiento máximo se obtiene con la L3 de 24 MB en 8 bancos de 3 MB.

Ampliaré el artículo con estas consideraciones,

Saludos,

Carlos.