D-TLB test de RMMA con tamaños hasta 16 MB. ¿Otra inflexión en 8192 KB?

¿Qué es el TLB?

.

.

.

.

El primer núcleo K8 (130 nm, 1 MB L2). Fuente: AMD. Pulsa para ampliar.

El primer núcleo K8 (130 nm, 1 MB L2). Fuente: AMD. Pulsa para ampliar..

.

- L1 D-TLB: 32 / 4 entradas. Full associative. Miss penalty de 5 ciclos.

- L1 I-TLB: 32/ 4 entradas. Full associative. Miss penalty de 4 ciclos.

- L2 D-TLB: 512 entradas. Asociatividad de 4 vías. Miss penalty de 17 ciclos.

- L2 I-TLB: 512 entradas. Asociatividad de 4 vías. Miss penalty de 25 ciclos.

.

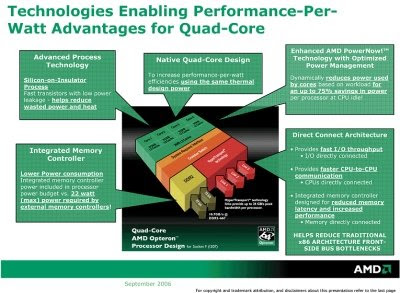

Arquitectura del AMD Barcelona Quadcore 65 nm.

.

Bloques funcionales del AMD Barcelona 65nm.

Implementación TLB en AMD Barcelona:

- L1 D-TLB: 48 entradas. Full associativity. Miss penalty 5 ciclos.

- L1 I-TLB: 48 entradas. Full associativity. Miss penalty 4 ciclos.

- L2 D-TLB: 512 / 128 entradas. Asociatividad 4 vías. Miss penalty 28 ciclos.

- L2 I-TLB: 512 / 128 entradas. Asociatividad 4 vías. Miss penalty 36 ciclos.

AMD y los 65 nm:

Este texto está tomado del siguiente artículo en este mismo sitio: http://lowlevelhardware.blogspot.com/2008/03/peculiaridades-microarquitectura-phenom.html.

Los micros Athlon64, inicialmente de 130nm, lograron una exitosa migración a los 90nm con el famoso núcleo Venice en los tiempos que Intel sufría con su core de 90nm, Prescott. Venice era mejor clock for clock respecto al Athlon64 original, consumía menos, escalaba mejor en frecuencia y dió a AMD una ventaja competitiva importante.

No sucedió lo mismo con la transición a 65nm. Actualmente los micros de mayor frecuencia de AMD todavía se fabrican con tecnología de 90nm (léase A64 6400+ a 3.2GHz, 2 L2 de 1MB). La misma CPU fabricada en 65nm (Brisbane 2L2 de 512KB) ráramente escala pasados los 3GHz (por otro lado Brisbane es algo más lento a la misma frecuencia).

Posiblemente sea la falta de recursos (económicos y técnicos) para la optimización y correcta migración al proceso de 65nm, pero estos son los hechos. Recordemos la bajísima capitalización actual de AMD (Nasdaq: AMD) en bolsa y la adquisición de ATI a un precio que luego se ha visto excesivo.

La gran superficie y alto coste del chip ha marcado el tamaño de sus cachés. La L2 es de 512 KB, cuando los Athlon64 de gama alta gozan de 1MB por procesador. En cuanto a la L3, solamente 2MB para cuatro núcleos se antoja una cantidad insuficiente, dado lo extendido del software multithread y el uso del PC en los sistemas operativos actuales. Esto es en parte compensado por su alta asociatividad de 32 vías que aumenta la tasa de aciertos.

Los K8 de 65nm, AMD Brisbane:

Brisbane es el stepping G del Athlon64 X2 AM2 con controladora de 128 bit DDR2 800, sustituye al stepping F, el primer AM2.

Todo el mundo conoce el hecho siguiente: un procesador AMD Athlon64 X2 de 65nm (core Brisbane) es más lento por ciclo que uno de la generación anterior de 90 nm. Empeora la velocidad de la caché L2, empeora su latencia y aumenta catastróficamente la latencia de memoria en accesos aleatorios (random).

¿Porqué es más lento Brisbane clock for clock que sus antecesores de 90 nm?

¿Qué ha ocurrido en la migración del núcleo K8 a 65nm?

¿A qué se debe el TLB bug de los primeros AMD Barcelona?

En la siguiente entrega analizamos el núcleo K8 en su variante de 90 nm, core Manchester. En la tercera analizaremos el core Barcelona que podemos encontrar en los Phenom y Opteron. quadcore de 65 nm.

Descarga de RMMa 3.8.

Página de DigitLife, desarolladores de RMMA.

No hay comentarios:

Publicar un comentario

Nota: solo los miembros de este blog pueden publicar comentarios.