Intel ha echado el resto en el diseño y realización efectiva de la caché L3 de su nuevo procesador Core i7, antes conocido como Nehalem.

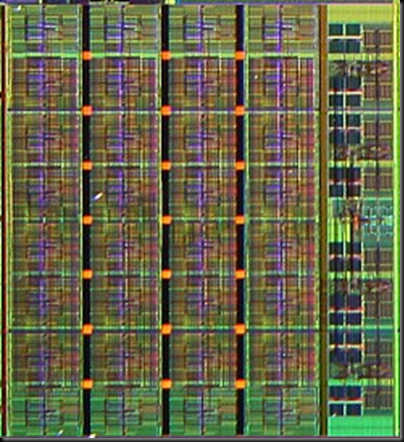

La caché L3 de Nehalem, como todos sabéis de 8 MB y asociatividad de 16 vías, es compartida entre los cuatro núcleos y de naturaleza inclusiva. Está dividida en cuatro arrays de 2 MB:

Array de 2 MB de L3 de Nehalem.

Siendo el tercer nivel de caché el número de peticiones que recibe de los cuatro procesadores a los que sirve se ve muy reducido debido a las pequeñas y rápidas L2 de 256 KB de 8 vías lo que permite no saturar su bus de datos. Pensemos que la tasa de aciertos de la L2 debe rondar el 80 - 90% dependiendo del software.

Pondré un ejemplo, en numeroso software comercial la caché L2 de un Core2Duo mantiene un 300% más de peticiones que la L2 de un Athlon64 X2.

Esto es debido a la mayor tasa de aciertos de las L2 de los A64 X2 en comparación con los Core2Duo por su mayor tamaño (64 - 64 KB contra 32 + 32 KB).

En este sentido podemos considerar la necesidad de la pequeña L2 en los procesadores Intel Core i7 como un medio para mitigar el tráfico desde y hacia la L3 que, recordemos, sirve a cuatro procesadores muy eficientes sedientos de datos e instrucciones.

La L3 en AMD Barcelona Phenom

En su día critiqué el ,para mi, mayor defecto de la microarquitectura del AMD K10: su asincronía y sobretodo sus abultadas latencias de sincronización.

El K10, en su actual modelo superior, el Phenom 9950 BE mantiene su L3 y controladoras de memoria a 2 GHz mientras que los cuatro núcleos procesan a 2.6 GHz.

Esto provoca unas latencias de L3 que rondan los 45 - 50 ciclos y más grave todavía un ancho de banda de L3 en lectura realmente mediocre debido a su raquítico bus interno de únicamente 64 bit como podemos observar en el cuadro siguiente.

| Lectura GB/s | Latencia ns | Latencia ciclos | |

| Caché L1 | 79.8 | 1.2 | 3 |

| Caché L2 | 20.0 | 3.7 | 10 |

| Caché L3 | 8.5 | 7.9 | 20 |

| Memoria | 8.0 | 55.0 | 138 |

El ingente equipo de arquitectos e ingenieros en Intel ha dado a luz un prodigio en forma de L3 para su nuevo procesador.

| Lectura GB/s | Latencia ns | Latencia ciclos | |

| Caché L1 | 51.2 | 1.2 | 4 |

| Caché L2 | 34.1 | 3.2 | 10 |

| Caché L3 | 18.2 | 5.7 | 18 |

| Memoria | 14.3 | 42.2 | 135 |

Resultados obtenidos con Everest 4.50 en un Intel Core i7 965 EE (3.2 GHz cores / 2.133 GHz L3 & MC) con 3 x DDR3 1066 7-7-7-20.

Si cambiamos la frecuencia del uncore a 2667 MHz (la nominal en el 965 EE) obtenemos ligeras mejoras en los datos de L3 y memoria principal:

| Lectura GB/s | Latencia ns | Latencia ciclos | |

| Caché L1 | 51.2 | 1.2 | 4 |

| Caché L2 | 34.1 | 3.2 | 10 |

| Caché L3 | 18.9 | 5.2 | 17 |

| Memoria | 14.9 | 39.0 | 125 |

Conclusiones:

Intel ha dotado a Nehalem de un uncore con buses bien dimensionados para no ahogar a sus potentes núcleos de procesamiento.

Unas matemáticas elementales nos indican que el bus de L3 de Nehalem debe ser de 128 bit:

(2.133 GHz * 128 bit) / (8 bit / 1 byte) = 34.8 GB/s

34.8 GB/s es el ancho de banda asignado por Intel al bus de L3 en los modelos Core i7 920 y 940, lo que le da un margen de ampliación considerable y supera con creces el ancho de banda de tres canales de DDR3 1066 (25.5 GB/s).

En el Extreme Edition 965:

(2.666 GHz * 128 bit) / (8 bit / 1 byte) = 42.656 GB/s

Supera el ancho de banda de un triple canal DDR3 1333 (32 GB/s). Como vemos las frecuencias de Uncore no han sido escogidas por Intel al azar, sino para dotar de margen al diseño y ha fijado su frecuencia por defecto en el doble (2X) del valor de frecuencia de la DDR3 utilizada.

En resumen, una gran flexibilidad y un buen margen de ampliación sobretodo teniendo en cuenta el reloj dinámico del uncore y su funcionamiento comprobado sin fallos hasta los 4 GHz para hacer frente a 3 canales DDR3 a 2 GHz a 1.65 V.

Ya han sido lanzadas las primeras unidades del Shanghai con resultados espectaculares,sobre todo en consumo.

ResponderEliminarDe momento vienen con bus DDR3 de 800 MHz(Hypertransport 1.0).

Habrá que esperar a principios de 2009 para ver los modelos con Hypertransport 3.0 a más de 41.6 GB/s.

AMD se está igualando a marchas forzadas con Intel.

Ahora veremos si realmente Intel "cumple" con los plazos de los servidores Nehalem.¿Habrá bugs?

Yo desde luego no lo descarto.