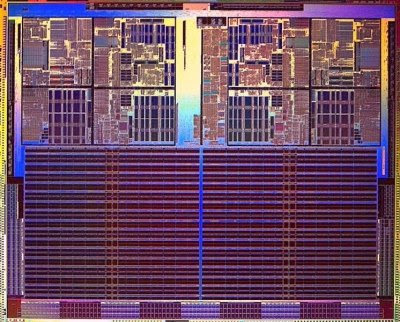

- Athlon64 X2 3800+ S939 Manchester (512 + 512 KB L2) @ 2.5 GHz.

- 2 x 1 GB Kingston HyperX DDR 400 @ 2.5 3 3 8 1T.

- Frecuencias de memoria: 416 MHz dual channel.

Resultados RMMA 3.8:

RMMA D-TLB test. Pulsa para ampliar.

RMMA D-TLB test. Pulsa para ampliar.Vemos el comportamiento normal:

- Hasta los 32 bloques actúa el L1 D-TLB con su bajísima latencia (unos 3 ciclos totales)

- De 32 a 512 bloques actúa el L2 D-TLB con unos 8 ciclos de latencia.

De aquí en adelante empieza el comportamiento anómalo:

- De 512 bloques en adelante la latencia va aumentando hasta estabilizarse en unos 40 ciclos en el rango de los 1536 a 8192 bloques. ¿Será un L3 D-TLB? Pero si no hay caché L3, este super-TLB se encuentra en la controladora de memoria y tiene una miss penalty de más de 100 ciclos, es decir, en caso de fallo se incurre en una penalización en el cálculo de la dirección física de memoria de más de 100 ciclos.

- De 8192 bloques en adelante la latencia aumenta hasta los 200 ciclos aproximadamente.

Funcionamiento de los niveles de TLB:

- Si se da un fallo de L1 D-TLB y un acierto de L2 D-TLB se acumula una latencia de 5 ciclos, resultando una latencia total de unos 8 ciclos (latencia caché L1 + L1 D-TLB miss penalty).

- Si se da un fallo de L2 D-TLB se acumula una latencia de unos 17 ciclos más, dando una latencia efectiva máxima de unos 40 ciclos.

Como podemos ver hay alguna estructura fuera del núcleo de ejecución que reduce la penalización del fallo del L2 D-TLB hasta un tamaño de 8192 bloques a un máximo de solamente unos 40 ciclos.

Por encima de los 8192 bloques la latencia aumenta hasta los 200 ciclos, típica latencia de acceso a memoria en modo aleatorio (random) con fallo de TLB.

RMMA I-TLB test. Pulsa para ampliar.

RMMA I-TLB test. Pulsa para ampliar.

En el caso del I-TLB los resultados son análogos, con latencias algo superiores.

Conclusiones:

La controladora de memoria de los microprocesadores Athlon64 X2 en su versión de 90 nm contiene un gran TLB, eficaz tanto en operaciones con datos como con instrucciones y con un tamaño efectivo de unos 8192 Bloques.

Su missprediction penalty es mayor de 100 ciclos, pero siendo sinceros, su tasa de fallos debe ser ínfima, cercana a cero.

Ahora nos queda resolver el enigma de las bajas prestaciones de Brisbane y el origen del TLB bug de los Barcelona stepping B1 y B2. Serán cuestiones para el siguiente artículo.

Tengo una duda, el TLB sólo actúa con la caché de datos? o también actúa sobre la de instrucciones? (ambas de nivel 1)

ResponderEliminarLuís,

ResponderEliminarUn TLB puede actuar sobre datos o sobre instrucciones o sobre ambos. En estas CPUs había un iTLB y un dTLB.

Saludos,

Carlos Yus.